3D NAND为实现四级单元提供了可行性

关于四级单元闪存纠错问题的潜在解决方法。

与此前的平面NAND相比,3D NAND技术的运用将使得错误检查代码更易于实现,这也进一步确定了容量提升的四级单元技术的可行性。

错误检查代码(ECC)技术的使用范围包括通过采用算法以计算为存储数据添加冗余所需添加与使用的位数,在固定大小区域内工作的分组代码与Reed-Solomon编码即是此类技术的应用实例。并且与该技术能够完成的纠错量相比,其可检测到的错误数量更多。

低密度奇偶校验(LDPC)编码是ECC技术的一种较新版本。BCH(Bose-Chaudhuri-Hocquenghem)编码则是另一项纠错技术,这种二进制BCH编码可被设计用于多位数纠错。通常而言,客户希望能够完成的纠错位数越多,则需要添加到数据中的冗余ECC位数就越多。

由于读取单元无法提供明确的1或0,因此在这种情况下,一个或多个字节的值可能会因错误而失真,所以NAND闪存需要配有ECC。

而ECC编码则能够检测并纠正以上所提及的错误。

随着NAND读取难度的增加,需要添加的ECC位数与ECC算法的复杂程度也随之提高。其中,“读取难度”一种概括性说法,其具体是指单元可读性随着单元尺寸与其所存储的位数增加而降低。

举例而言,小单元之间可能存在跨区效应,具体表现为一个单元内的设置值可能会对相邻单元内的设置造成一定影响。而其中所涉及的设置值还包括电子——其数量与稳定性会随着单元尺寸缩小而降低。

因此,与SLC(一级单元)相比,MLC(二级单元)与TLC(三级单元)闪存的读取固然会更困难。当然,尽管QLC(四级单元)在技术上已具有一定可行性,但由于单元可读性以及ECC编码与算法仍是亟待解决的两大难题,所以直到现在QLC还尚未具备实用性。

SanDisk公司曾于2009年试图采用43纳米几何平面结构实现QLC NAND的生产,但在经历了一年左右的研究后即选择了放弃。

同样,与25纳米单元以及35纳米单元相比,20纳米的MLC闪存单元更难实现读取。此外,16纳米的MLC闪存单元则是很难实现再次读取,而在此级别上所采用的ECC已经实现了BCH与LDPC ECC技术的融合。

根据Objective Analysis公司的Jim Handy简要报告可知,选择采用3D NAND将会让这些难题简化。

其中的两大主要原因如下:

首先,当3D NAND闪存芯片建成之后,单元尺寸将从15纳米恢复至40纳米左右,尔后即可在该芯片上采用最先进的2D或平面NAND技术。

其次则是源于3D NAND的构建方式。“3D NAND的浮栅或电荷捕获将在作为通道的接杆附近形成一个圆圈,从而让其面积增加了三倍以上。故而现在3D NAND芯片的面积大致相当于一款90纳米的平面NAND芯片。”

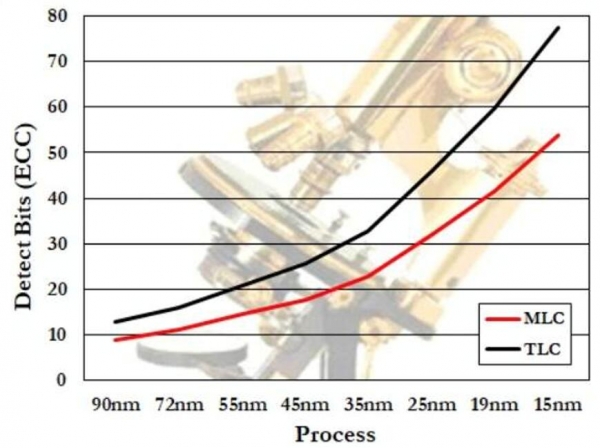

另外,Jim Handy还提供了一张图表以展示MLC与TLC闪存在不同单元尺寸条件下通常所需的ECC位数。

根据图表显示,TLC NAND闪存的单元尺寸在15纳米工艺几何尺寸时所需ECC位数已超过75比特,而当芯片的几何尺寸为90纳米时,ECC的位数需求则在15以下。

对此,Handy在其报告中写道:“我们据此即可推断QLC 3D NAND所需的位数将少于20。这也是为何与以往的平面NAND相比,采用3D NAND能够提升QLC可行性的原因。”

此外,Handy还描绘了每单元拥有更多位数的前景。“从长远看来,我认为大多数3D NAND控制器将会采用LDPC以确保每单元存储4字节以上的数据。当然,实现这一目标需要一些时间。而在短期内,3D NAND将能够通过使用简单的BCH算法完成其向QLC转变。”

试想每单元能够存储5比特字节的闪存——或称之为五级单元或PLC闪存?由于QLC已经用于代表四级单元闪存,所以我们不能将五级单元按quintuple level cell首字母缩写命名,并且其将比QLC闪存增加25%,每单元存储为5比特而非4比特。因此,一款容量为1 TB的QLC SSD或将可能变为1.25 TB的PLC SSD。恩,此番前景的确令人欣喜,但或许仍需数年才能得以实现。

目前看来,QLC闪存似乎已具备一定的可行性,我们或将于今年年底便可见其真身。

好文章,需要你的鼓励

《数字经济洞察周报》2024年第2期 |智谱AI技术开放日发布GLM-4大模型

智谱AI发布GLM-4大模型;工信部发布《国家人工智能产业综合标准化体系建设指南》(征求意见稿);高通骁龙数字底盘、联想AI PC亮相CES 2024

《数字经济洞察周报》2024年第1期 |17部门联合印发《“数据要素x”三年行动计划(2024—2026年)》

国家数据局等17部门联合印发《“数据要素x”三年行动计划(2024—2026年)》;小米举办汽车技术发布会。

英特尔至强和AI PC等产品为Meta Llama 3生成式AI工作负载提供加速

万字梳理中国AIGC产业峰会激辩,大模型应用最全行业参考在此

Galaxy AI从Galaxy S24系列进一步扩充支持到更多设备

以AI对抗AI,抵御AI时代欺诈风暴

“元脑”品牌全面升级!浪潮信息全力进击人工智能

数智范式会展发布《长三角制造业数字化建设需求侧市场研究报告》,成功举办“智造未来·高峰对话”论坛

SAP携手梅赛德斯-AMG 马石油 F1 车队,亮相F1中国大奖赛

F1联想中国大奖赛前夕,ThinkBook举办AI PC新品抢先试驾夜

Limitless推出一款AI加持的可穿戴录音笔

华为邵士新:iMaster NCE构筑“一图一脑”,加速FBB迈向高阶自智

英特尔与生态伙伴紧密合作,OPS 2.0标准助力智慧教育再升级

引领大模型创新实践,加速迈向高阶自智网络

软件定义存储中,企业级SSD扮演了什么角色?

从决策式AI进阶到生成式AI,SSD将变得更为重要

AI发展打破存储波动周期,Solidigm引领下QLC NAND SSD遍地开花

Solidigm亮相中国闪存市场峰会:丰富产品组合打造AI时代存力底座

美光推出业界领先的紧凑封装型 UFS,助力下一代智能手机设计搭载更大容量电池

近线HDD将成独苗,其他磁盘驱动器或将于2028年退出历史舞台

多元化发展 盘点SMI慧荣2023年有哪些SSD新技术、新产品

面向AI、云时代的存储需求,西部数据给出不一样的思考!

面对SSD竞争压力,2023年硬盘容量迎来小幅提升

对话平头哥:突破SSD主控芯片,触发新一轮市场冲击波